design of asynchronous sequential circuits

|

Esign of asynchronous sequential circuits

There are two distinct models by which a synchronous sequential logic circuit can be designed In Mealy Model the output is derived from present state as well |

|

Unit iv asynchronous sequential logic

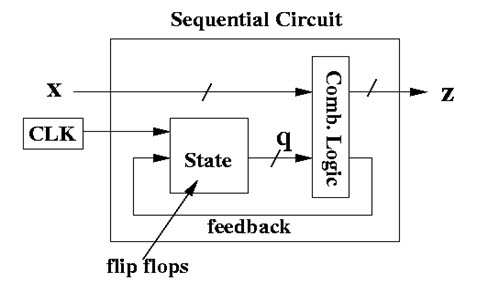

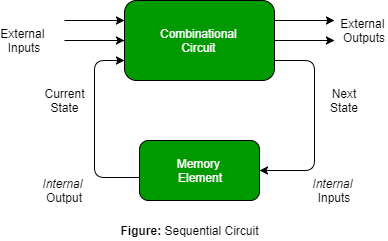

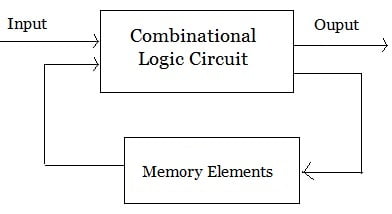

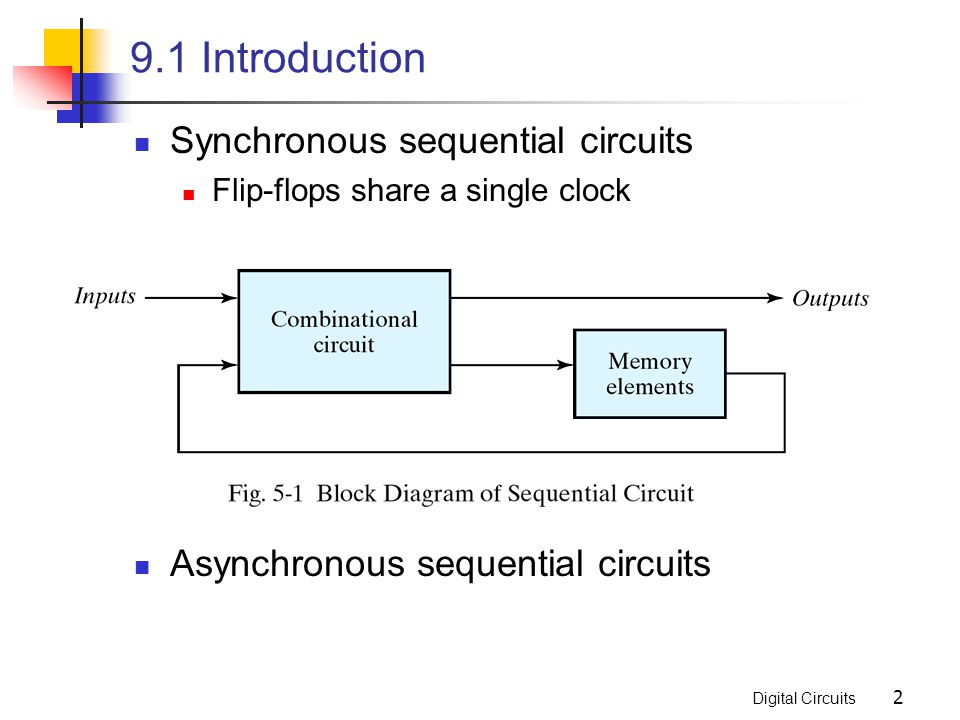

Introduction • A sequential circuit is specified by a time sequence of inputs outputs and internal states The output changes whenever a clock |

|

Asynchronous Sequential Circuits Design

Sequential circuits are those which use previous and current input variables by storing their information and placing them back into the circuit on the next |

|

Asynchronous Sequential Circuits

-The design of these circuits is more difficult than the design of synchronous circuits due to the timing problem Page 4 Why Asynchronous Circuits? |

Analysis and Design of Sequential circuits:

Reduce states using state reduction technique.

Verify the number of Flip-Flops and type of Flip-Flop to be used.

Derive the excitation equations using the excitation table.

Derive the output function and the Flip-Flop input functions.

What is the analysis and design procedure of asynchronous sequential circuits?

The general steps to be followed for design of asynchronous sequential circuits are as follows :

1Create a state table or state diagram from the given problem statement.2) Create a new reduced state table by removing all the redundant states.

3) Create the transition table.

What is the design approach to asynchronous circuits?

Asynchronous circuit design is characterized by the use of function blocks, asynchronous registers, and the absence of clock signals.

This means that the counters in asynchronous circuits do not receive inputs simultaneously, nor do they give outputs simultaneously.

How does an asynchronous sequential circuit work?

Asynchronous circuit (clockless or self-timed circuit) is a sequential digital logic circuit that does not use a global clock circuit or signal generator to synchronize its components.

Instead, the components are driven by a handshaking circuit which indicates a completion of a set of instructions.

|

Chapter 22 - Asynchronous Sequential Circuits

We will look at the relation of setup and hold time to the design of the asynchronous circuits that realize flip-flops in more detail in Chapter 23. In |

|

A DESIGN METHOD OF ASYNCHRONOUS SEQUENTIAL

A systematic asynchronous design method based on a flow diagram is shown. The realization utilizes a so-called phase-register coded lout of 11. |

|

CS8351 DIGITAL PRINCIPLES AND SYSTEM DESIGN UNIT IV

The analysis of asynchronous sequential circuits consists of obtaining a table or a diagram that describes the sequence of internal states and outputs as a |

|

Asynchronous Sequential Circuits Design

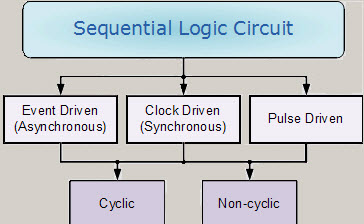

Asynchronous sequential circuits do not use clock signals as synchronous circuits do. Instead the circuit is driven by the pulses of the inputs which means |

|

Asynchronous Sequential Circuits

The delay elements can be viewed as providing short term memory for the sequential circuit. Page 3. Asynchronous Sequential Circuits. • During the design of |

|

IE1204 Digital Design F12: Asynchronous Sequential Circuits (Part 1)

Asynchronous Mealy compatible. IE1204 Digital Design Autumn2016. ·Asynchronous sequential circuits have similar structure as synchronous sequential circuits. · |

|

A Modern Approach to the Asynchronous Sequential Circuit Synthesis

The switching circuit design is composed of the two classes of the devices: combinational circuits and sequential circuits. The class of the sequential circuits. |

|

Pass-transistor asynchronous sequential circuits

Abstract -The vast majority of sequential circuits currently imple- mented with VLSI circuit technology are designed using synchronous design theory. |

|

Design of asynchronous esign of asynchronous sequential circuits

There are two distinct models by which a synchronous sequential logic circuit can be designed. In Mealy Model the output is derived from present state as well |

|

COE 202: Digital Logic Design Sequential Circuits Part 1

• Latches are useful in asynchronous sequential circuits. • Flip-Flips are built with latches. Page 8. Latches. • A latch is binary storage element. • Can store |

|

Design of asynchronous esign of asynchronous sequential circuits

There are two distinct models by which a synchronous sequential logic circuit can be designed. In Mealy Model the output is derived from present state as well |

|

IE1204 Digital Design F12: Asynchronous Sequential Circuits (Part 1)

gates and summarize their delays to a single block with delay ?. Asynchronous sequential circuit: SR-latch with NOR gates. IE1204 Digital Design Autumn2016. |

|

Asynchronous Sequential Circuits

The analysis of asynchronous sequential circuits An asynchronous sequential circuit may become ... Design a gated latch circuit with two inputs G. |

|

Chapter 22 - Asynchronous Sequential Circuits

Design a toggle circuit like the one in Section 22.2 except that pulses on the input alternate over three outputs. 22–6 Three-Way Edge Toggle. Page 12. 394. |

|

State assignments for non-normal asynchronous sequential circuits

designing an asynchronous sequential circuit is obtaining an internal state assignment. The internal state assignment problem consists basically of encoding |

|

Chapter 9 - Asynchronous Sequential Logic

the behavior of the circuit can be analyzed by observing the stale transition as a function of changes in the input variables. Flow Table. During the design of |

|

CS8351 DIGITAL PRINCIPLES AND SYSTEM DESIGN UNIT IV

The memory elements in asynchronous sequential circuits are either unclocked flip-flops (Latches) or time-delay elements. 3. Page 4. S No. Synchronous |

|

Chapter 9 Asynchronous Sequential Logic Outline

Asynchronous Sequential Circuits. ? Analysis Procedure. ? Circuits with Latches. ? Design Procedure. ? Reduction of State and Flow Tables. |

|

Using Petri Nets in the Design Process for Interacting Asynchronous

Each asynchronous sequential circuit can be described by a state tranllition graph and the .'~e . ign of the circuit froro the given graph is routine. |

|

Asynchronous Sequential Circuits

The delay elements can be viewed as providing short term memory for the sequential circuit. Page 3. Asynchronous Sequential Circuits. • During the design of |

|

Asynchronous Sequential Circuits

Asynchronous sequential circuits have state that is not synchronized with a clock Like the synchronous sequential circuits we have studied up to this point they are realized by adding state feedback to combinational logic that imple- ments a next-state function |

|

Chapter 9 Asynchronous Sequential Logic Outline

Asynchronous Sequential Circuits ▫ Analysis Procedure ▫ Circuits with Latches ▫ Design Procedure ▫ Reduction of State and Flow Tables ▫ Race- Free |

|

Appendix 1 Asynchronous Sequential Logic Design

A block diagram of a sequential circuit or machine is shown in figure Al l Inputs = == Combinational I==:> Outputs Logic Memory Internal States ~- |

|

IE1204 Digital Design F12: Asynchronous Sequential Circuits (Part 1)

gates and summarize their delays to a single block with delay Δ Asynchronous sequential circuit: SR-latch with NOR gates IE1204 Digital Design, Autumn2016 |

|

Asynchronous Sequential Circuits

From a logic diagram, Boolean expressions are written and then transferred into tabular form An example of an asynchronous sequential circuit is shown below : |

|

Design of asynchronous esign of asynchronous sequential circuits

There are two distinct models by which a synchronous sequential logic circuit can be designed In Mealy Model, the output is derived from present state as well as |

|

Asynchronous Sequential Circuits Design - CCS University

Asynchronous sequential circuits do not use clock signals as synchronous circuits do Instead, the circuit is driven by the pulses of the inputs which means the state |

|

Asynchronous Circuits - Department of Electronics

asynchronous circuits and brie y explain some asynchronous design ments, instead of in latches or ip- ops, as synchronous sequential circuits do The design |

|

Synchronous Sequential Circuit

Have better performance but hard to design due to timing problems Why Asynchronous Circuits? ✓ Accelerate the speed of the machine (no need to wait for the |

![Chapter 9 Asynchronous Sequential Logic Outline - [PDF Document] Chapter 9 Asynchronous Sequential Logic Outline - [PDF Document]](https://slideplayer.com/slide/5005999/16/images/6/Examples+the+excitation+variables%3A+Y1+and+Y2+Fig.+9.2+Y1+%3D+xy1%2B+x+y2.jpg)

![HX_6776] Sequential Circuits In Digital Electronics Wiring Diagram HX_6776] Sequential Circuits In Digital Electronics Wiring Diagram](https://blog.oureducation.in/wp-content/uploads/2013/01/block1.gif)

![Chapter 9 Asynchronous Sequential Logic Outline - [PDF Document] Chapter 9 Asynchronous Sequential Logic Outline - [PDF Document]](https://www.tutorialspoint.com/computer_logical_organization/images/sequential_circuit_blockdiagram.jpg)

-Exam-Previous-Years-Question-Paper-5.jpg)